本篇内容包括两部分:

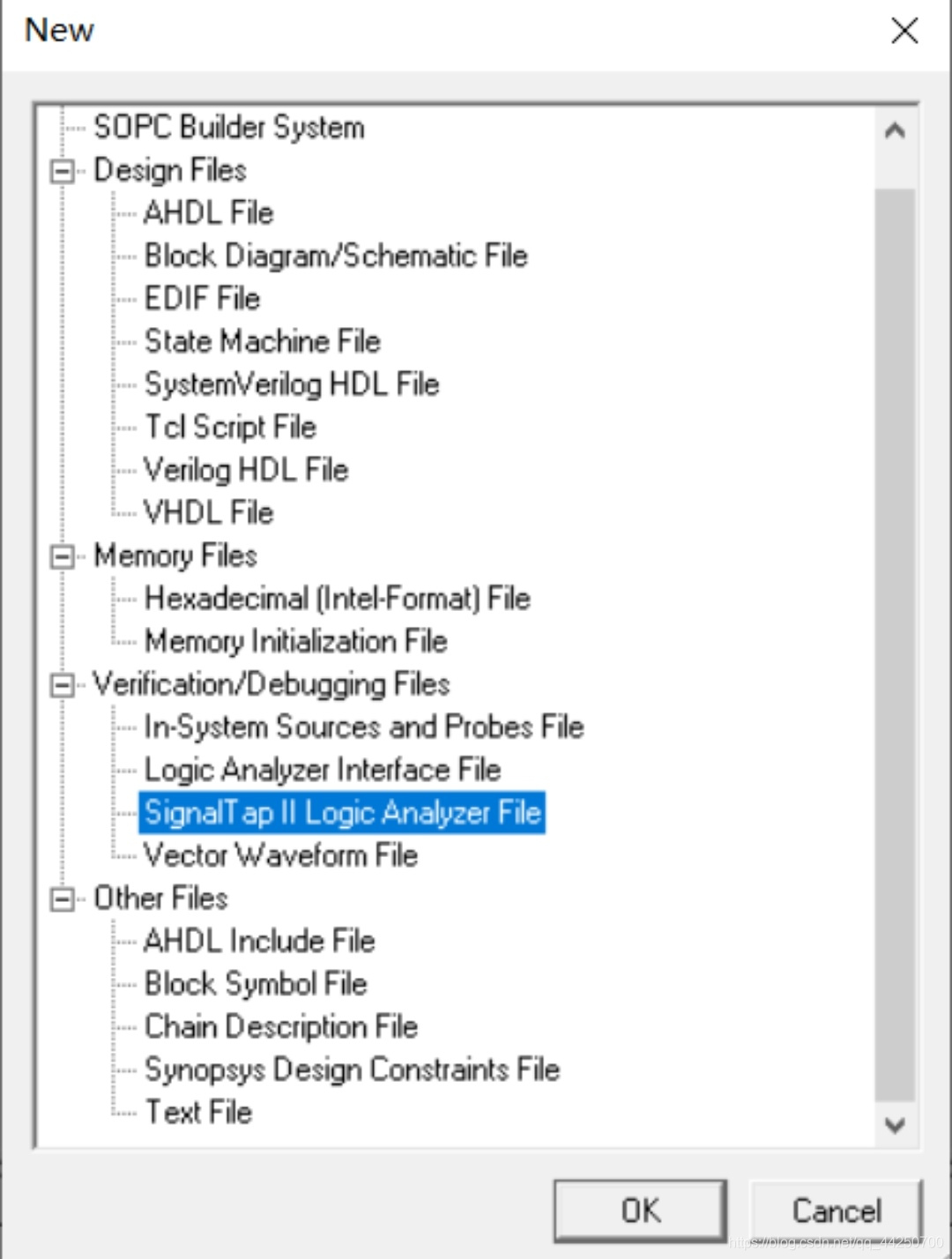

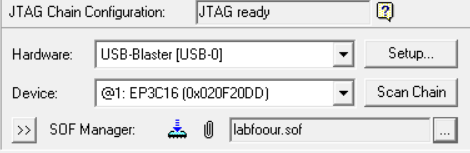

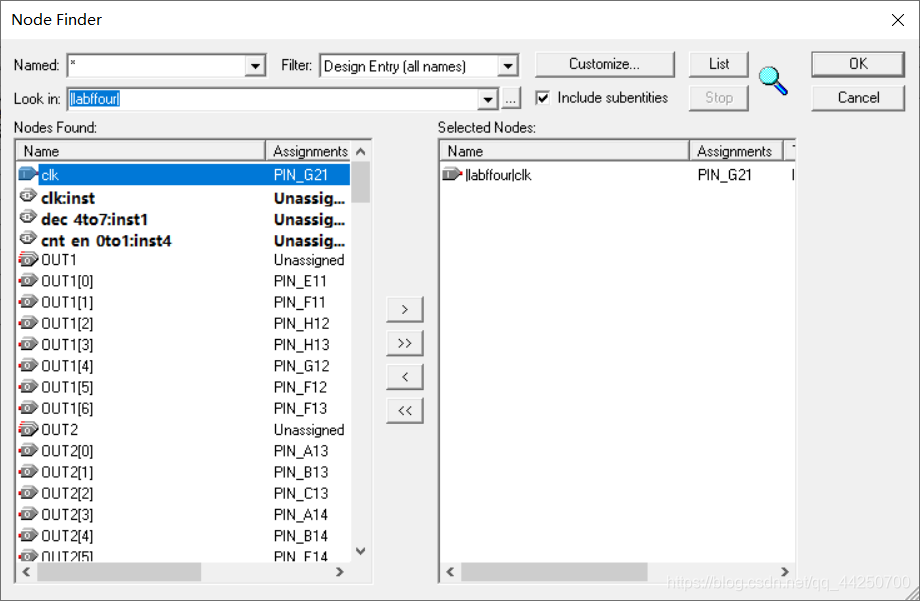

1、介绍一下Signal Tap如何抓取波形。

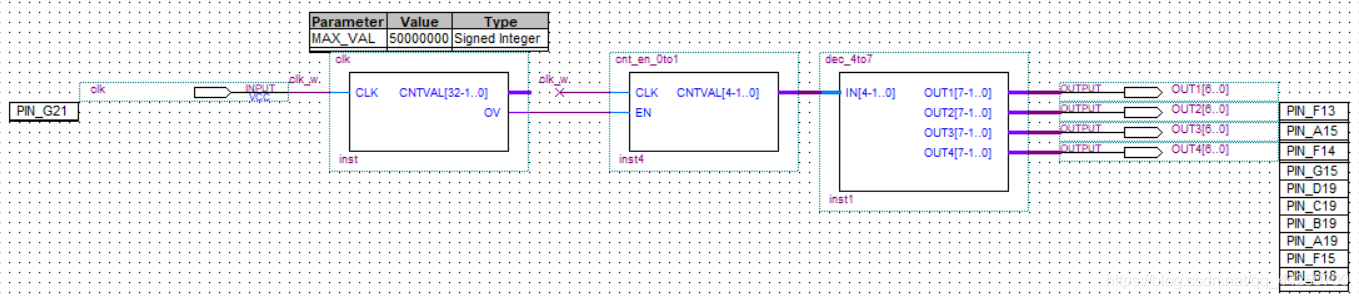

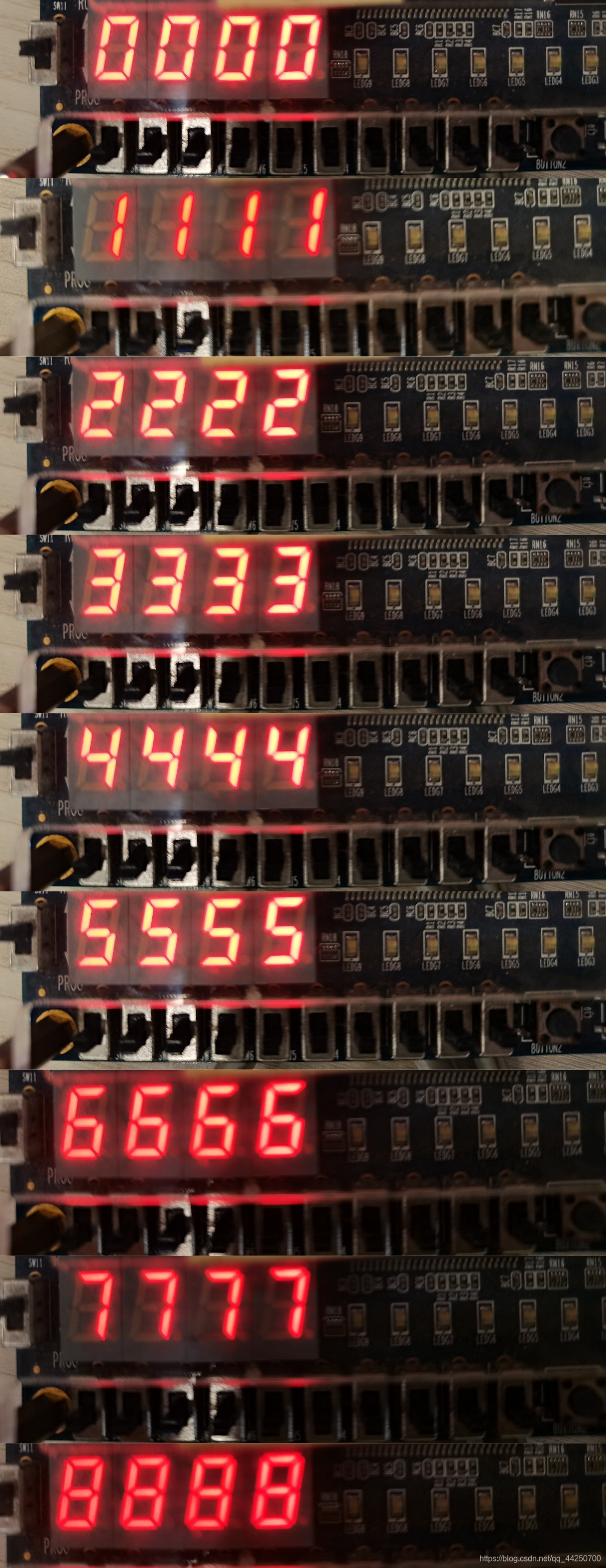

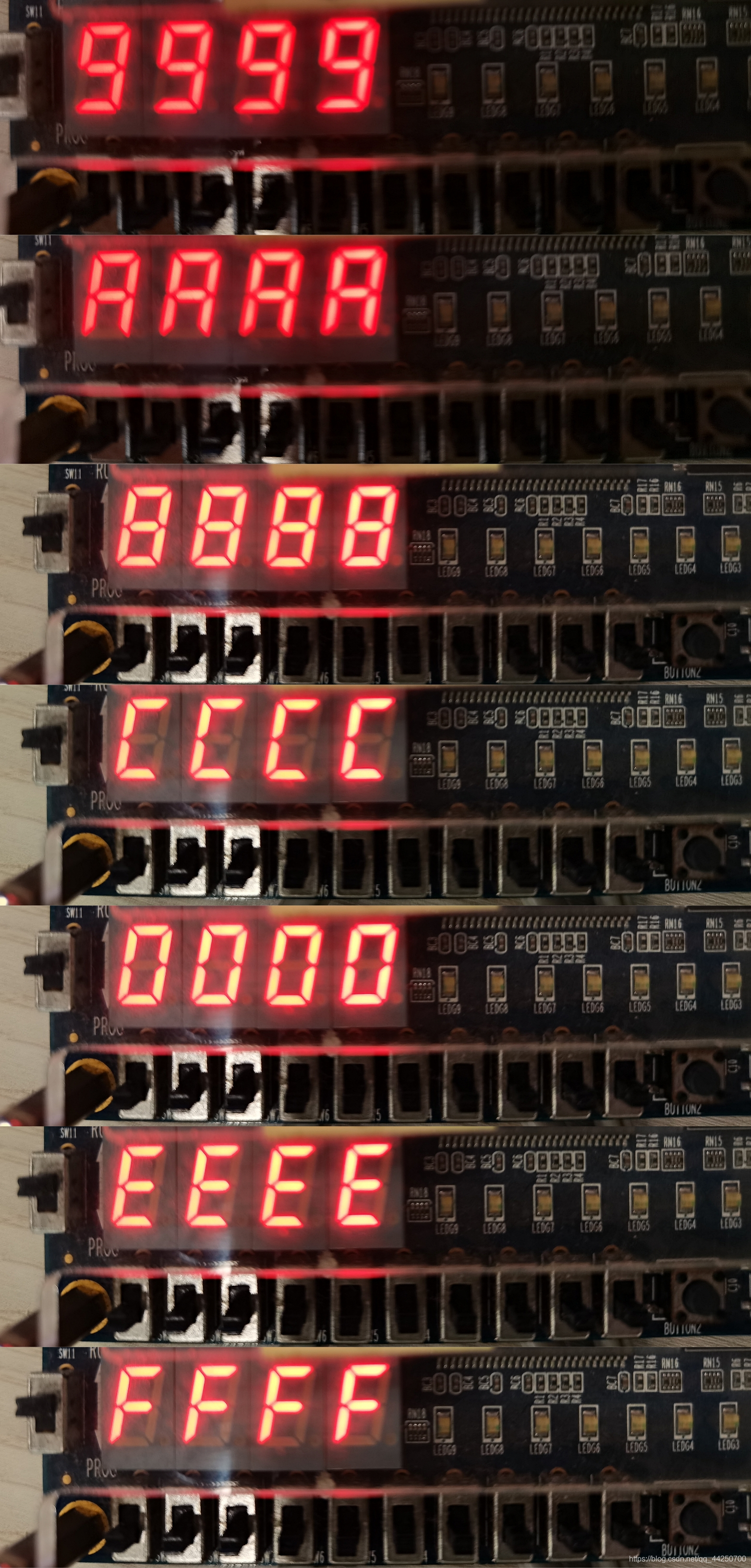

2、以我刚做完的实验为例(实现四个数码管以1HZ的频率进行跳变,从“0000”~“EEEE”一共16个状态的循环跳变),观察SignalTap波形抓取结果,并分析一下实验中遇到的问题以及解决办法。实验代码和BDF原理图会在篇末给出。

问题:当我点红色的小三角抓取波形的时候,发现没有波形,此时的Status 是绿色的Waiting for trigger,这是为什么呢?应该如何解决?

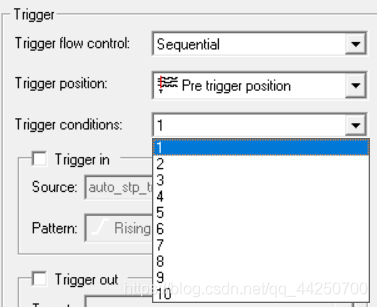

答: ①waiting for trigger的意思是没有达到触发条件。比如说我把OUT设为上升沿触发,那么只有当OUT出现上升沿时(比如由0变为1),SignalTap才会开始波形抓取,其余时间都是处于waiting for trigger状态,也就是陷入僵局。

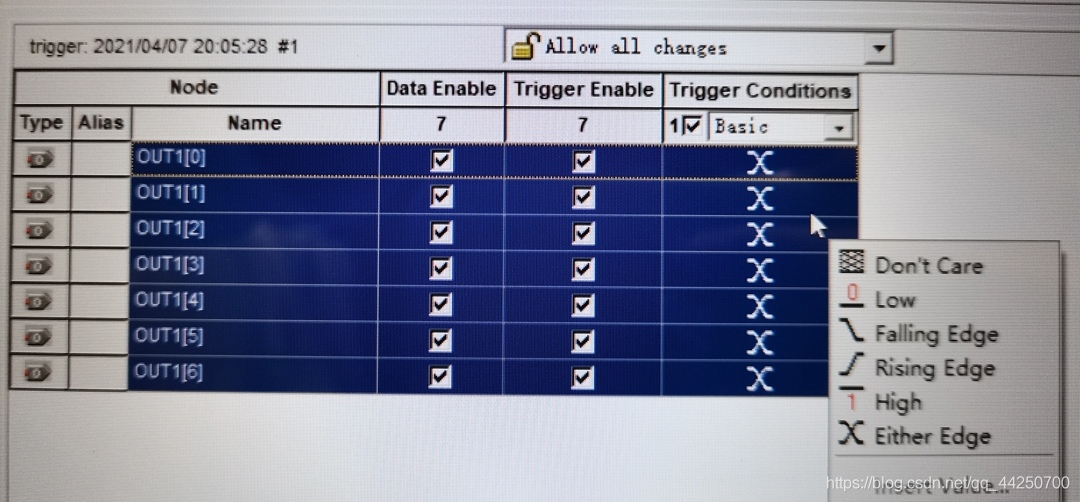

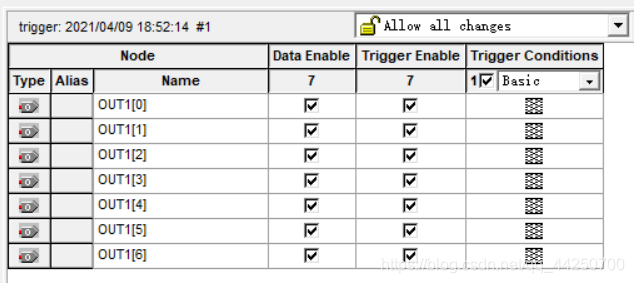

②因为在本实验的SignalTap中我添加了一组七段数码管的管脚OUT1[6…0],将它们trigger 设置的是Either Edge。那么只有当7个输出同时出现上升沿(0→1)或者同时出现下降沿(1→0)时,SignalTap才会开始波形抓取,否则就会一直Waiting for trigger。

③但经过分析发现,0→1→…→E→F变化时,7个输出并没有同时出现上升沿或下降沿,所以就会出现波形抓不出来的结果。

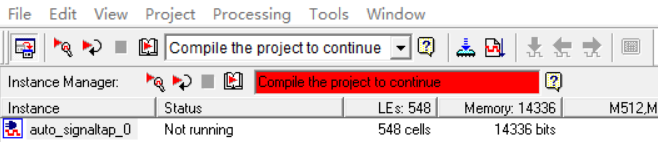

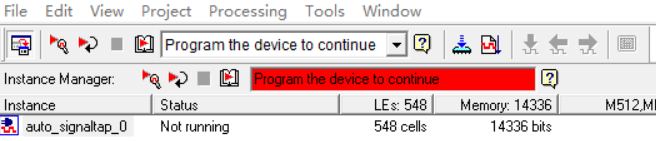

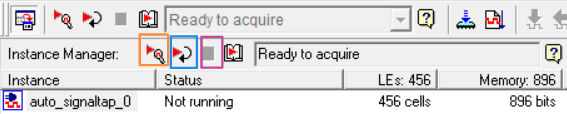

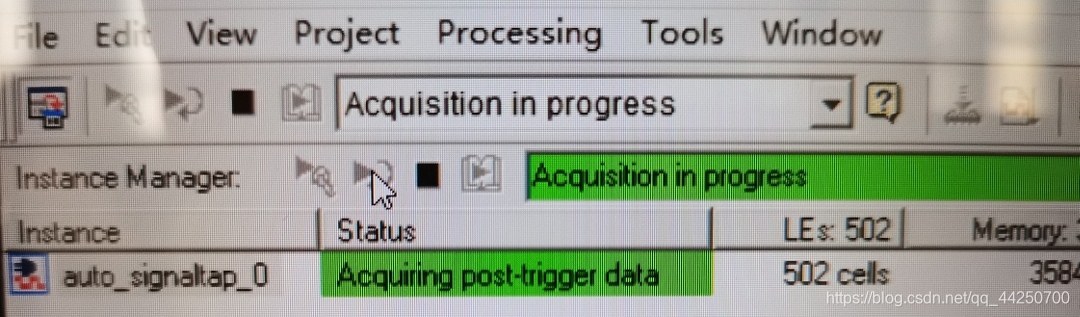

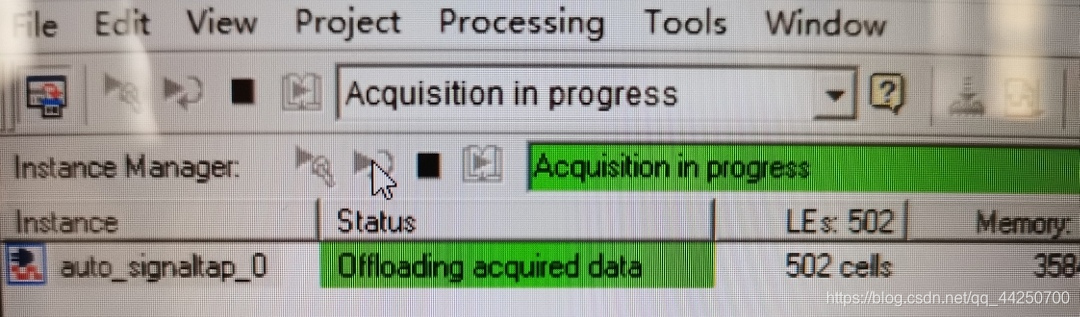

④为了验证我的猜想,现在我把OUT1[0]的trigger变为Rising Edge,把OUT1[6…1]变为Don’t care。点击带有旋转箭头的红色小三角进行波形抓取,发现只有当OUT1[0]从0变为1时,state为抓取数据的状态(如下图所示Acquiring post-trigger data、offloading acquired data),同时在下边的大框里可以看到抓出来的波形。其余时间都是waiting for trigger。

因此我的解决办法为:把7个输出的trigger全部改为Don’t care,也就是随即抓波形,不用等触发条件到才抓取。

点击红色小箭头抓取波形,成功!

如图所示是我抓到的一个波形,由逻辑值OUT1=7’b 1000000,可以知道抓到的这个是**“0”**的波形。每次点“单次运行”红色的小三角,都会抓到一个波形。点“连续运行”红色小三角就会看到波形的动态变化过程。

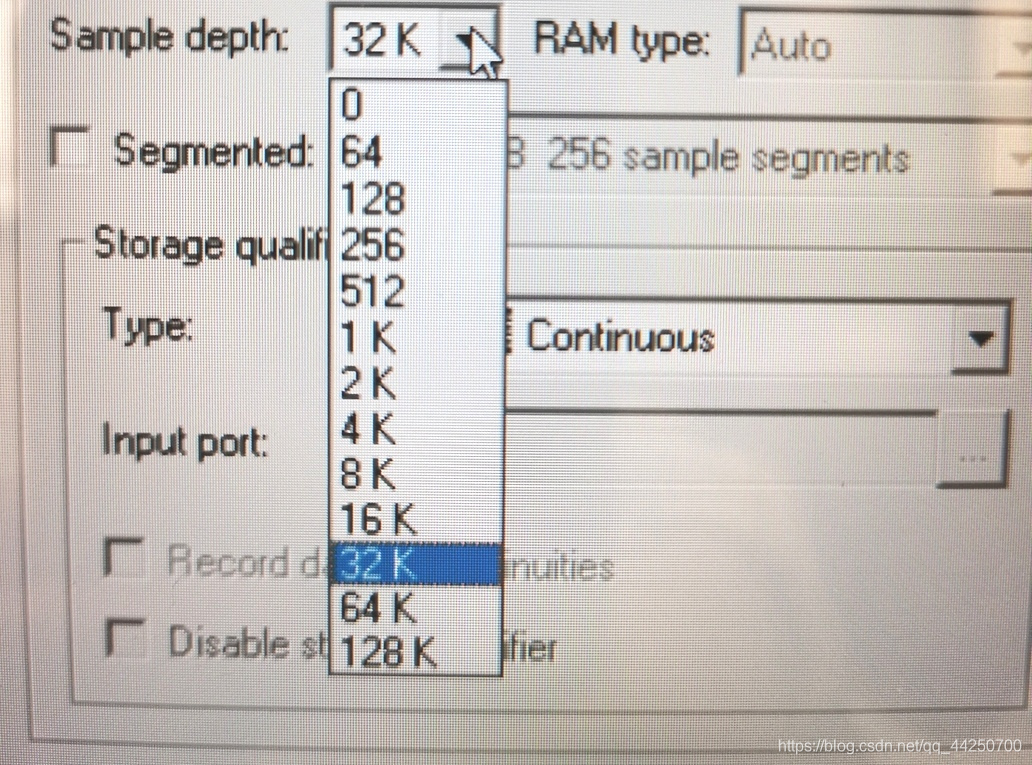

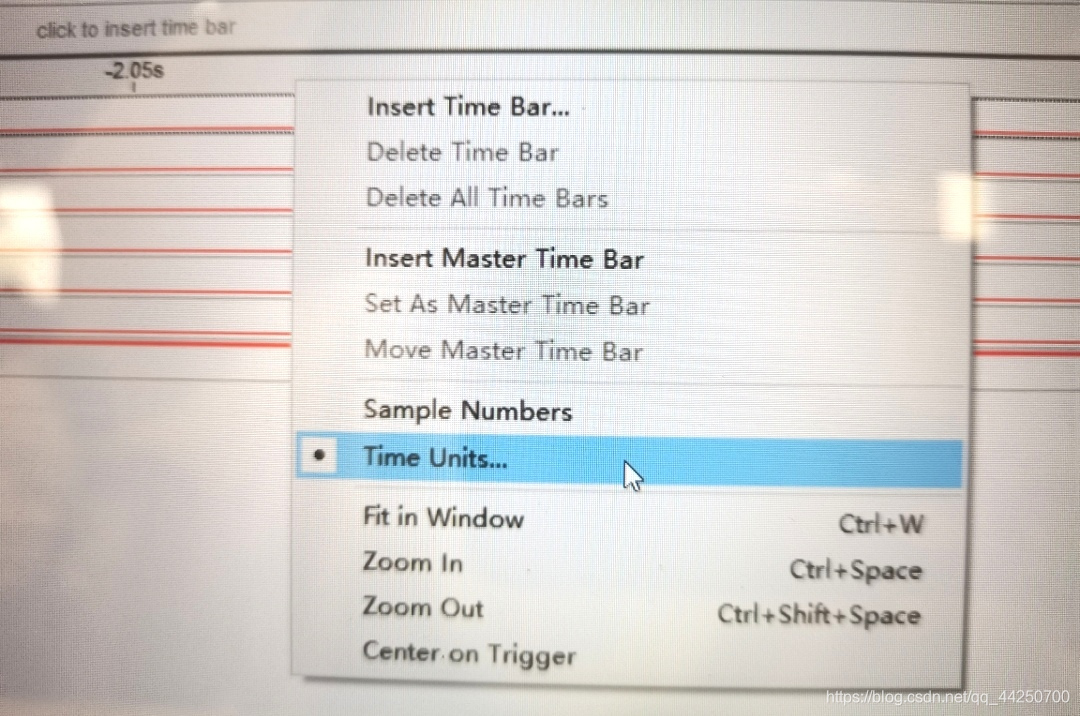

以下是我试过两种方法:

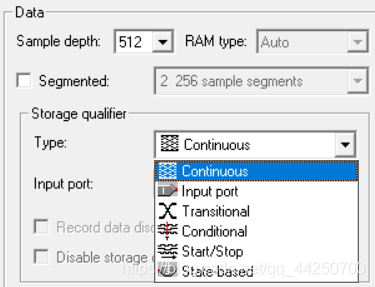

①增加采样点,即增加sample depth的值

②更改时间轴范围(如下图)

代码

module clk(

CLK , // clock

CNTVAL, // counter value

OV ); // overflow

input CLK;

output [32-1:0] CNTVAL;

output OV;

parameter MAX_VAL = 500_000;

reg [32-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(CNTVAL >= MAX_VAL)

CNTVAL <= 0;

else

CNTVAL <= CNTVAL + 1'b1;

end

always @ (CNTVAL) begin

if(CNTVAL == MAX_VAL)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule

//

module cnt_en_0to1(

CLK , // clock

CNTVAL, // counter value

EN ,);

input CLK;

input EN;

output [4-1:0] CNTVAL;

reg [4-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(EN) begin // work enable

if(CNTVAL >= 15)

CNTVAL <= 0;

else

CNTVAL <= CNTVAL + 1'b1;

end

else

CNTVAL <= CNTVAL ; // hold same value

end

endmodule

module dec_4to7(

IN ,

OUT1,

OUT2,

OUT3,

OUT4);

input [4-1:0]IN;

output [7-1:0] OUT1 ;

output [7-1:0] OUT2 ;

output [7-1:0] OUT3 ;

output [7-1:0] OUT4 ;

reg [7-1:0] OUT1 ;

reg [7-1:0] OUT2 ;

reg [7-1:0] OUT3 ;

reg [7-1:0] OUT4 ;

always @ (IN) begin

case(IN)

4'b 0000: OUT1 = 7'b 1000000;

4'b 0001: OUT1 = 7'b 1111001;

4'b 0010: OUT1 = 7'b 0100100;

4'b 0011: OUT1 = 7'b 0110000;

4'b 0100: OUT1 = 7'b 0011001;

4'b 0101: OUT1 = 7'b 0010010;

4'b 0110: OUT1 = 7'b 0000010;

4'b 0111: OUT1 = 7'b 1111000;

4'b 1000: OUT1 = 7'b 0000000;

4'b 1001: OUT1 = 7'b 0010000;

4'b 1010: OUT1 = 7'b 0001000;

4'b 1011: OUT1 = 7'b 0000000;

4'b 1100: OUT1 = 7'b 1000110;

4'b 1101: OUT1 = 7'b 1000000;

4'b 1110: OUT1 = 7'b 0000110;

4'b 1111: OUT1 = 7'b 0001110;

endcase

case(IN)

4'b0000: OUT2 = 7'b 1000000;

4'b0001: OUT2 = 7'b 1111001;

4'b0010: OUT2 = 7'b 0100100;

4'b0011: OUT2 = 7'b 0110000;

4'b0100: OUT2 = 7'b 0011001;

4'b0101: OUT2 = 7'b 0010010;

4'b0110: OUT2 = 7'b 0000010;

4'b0111: OUT2 = 7'b 1111000;

4'b1000: OUT2 = 7'b 0000000;

4'b1001: OUT2 = 7'b 0010000;

4'b1010: OUT2 = 7'b 0001000;

4'b1011: OUT2 = 7'b 0000000;

4'b1100: OUT2 = 7'b 1000110;

4'b1101: OUT2 = 7'b 1000000;

4'b1110: OUT2 = 7'b 0000110;

4'b1111: OUT2 = 7'b 0001110;

endcase

case(IN)

4'b0000: OUT3 = 7'b 1000000;

4'b0001: OUT3 = 7'b 1111001;

4'b0010: OUT3 = 7'b 0100100;

4'b0011: OUT3 = 7'b 0110000;

4'b0100: OUT3 = 7'b 0011001;

4'b0101: OUT3 = 7'b 0010010;

4'b0110: OUT3 = 7'b 0000010;

4'b0111: OUT3 = 7'b 1111000;

4'b1000: OUT3 = 7'b 0000000;

4'b1001: OUT3 = 7'b 0010000;

4'b1010: OUT3 = 7'b 0001000;

4'b1011: OUT3 = 7'b 0000000;

4'b1100: OUT3 = 7'b 1000110;

4'b1101: OUT3 = 7'b 1000000;

4'b1110: OUT3 = 7'b 0000110;

4'b1111: OUT3 = 7'b 0001110;

endcase

case(IN)

4'b0000: OUT4 = 7'b 1000000;

4'b0001: OUT4 = 7'b 1111001;

4'b0010: OUT4 = 7'b 0100100;

4'b0011: OUT4 = 7'b 0110000;

4'b0100: OUT4 = 7'b 0011001;

4'b0101: OUT4 = 7'b 0010010;

4'b0110: OUT4 = 7'b 0000010;

4'b0111: OUT4 = 7'b 1111000;

4'b1000: OUT4 = 7'b 0000000;

4'b1001: OUT4 = 7'b 0010000;

4'b1010: OUT4 = 7'b 0001000;

4'b1011: OUT4 = 7'b 0000000;

4'b1100: OUT4 = 7'b 1000110;

4'b1101: OUT4 = 7'b 1000000;

4'b1110: OUT4 = 7'b 0000110;

4'b1111: OUT4 = 7'b 0001110;

endcase

end

endmodule

BDF原理图

fpga板子结果

--------------------------------- 完 ---------------------------------

目前管理信息系统已从传统的客户机/服务器(C/S)模式转向了浏览器/服务器(B/S...

sudo 表示 superuser do,它允许已验证的用户以其他用户的身份来运行命令。其他...

我在Window XP中安装了Gvim7.2,然后桌面上出现了三个快捷方式,gvim72.exe,gvim...

我们都知道,保护敏感信息至关重要。幸运的是,现在大多数企业都拥有可靠的网络...

本文实例讲述了ThinkPHP5框架中使用JWT的方法。分享给大家供大家参考,具体如下...

Asp.Net母版页的相关知识 母版页的使用与普通页面类似,可以在其中放置文件或者...

JavaScript基础入门 1、快速入门 1.1 引入script 内部标签 script / script 外部...

由于我这边的网络原因,没用从FCK的官网下载到源码... 这套源码是FCK2.2版反编译...

本文实例讲述了Java Web开发之MD5加密用法。分享给大家供大家参考。具体如下: M...

声明式API vs 命令时API 计算机系统是分层的,也就是下层做一些支持的工作,暴露...