四川师范大学工学院·徐浩宇

2021.4.19

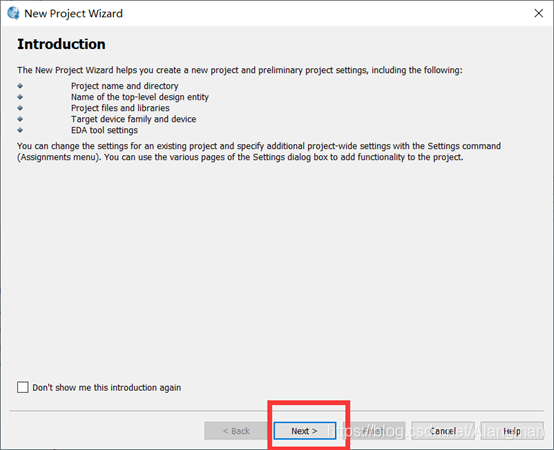

点击新建一个工程

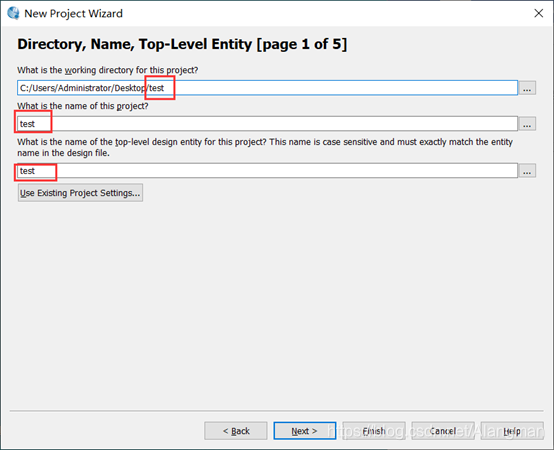

选择工程保存的路径,填写工程名称,注意,三个圈起来的应该相同

与上一步的文件名也相同;

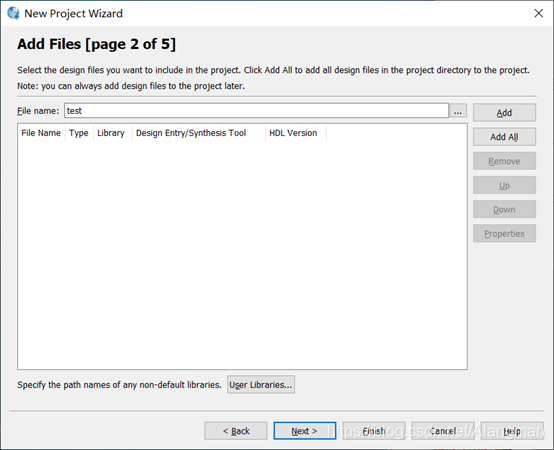

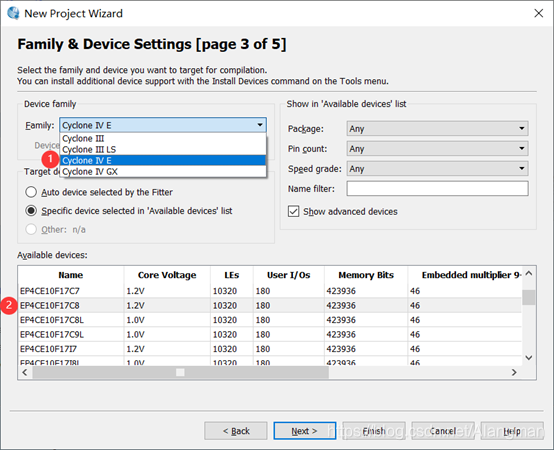

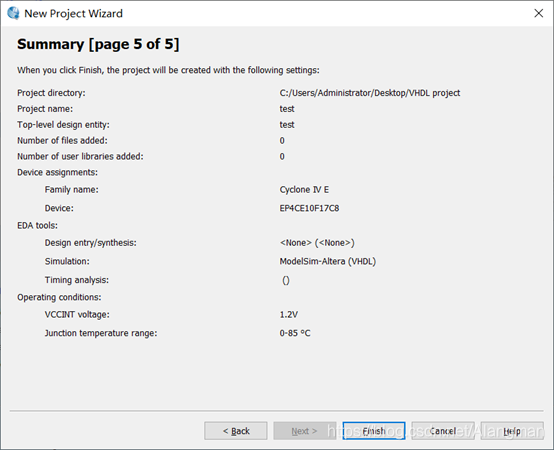

选择设备类型,一定要进行选择,否则后面编译仿真时可能会出错

我们使用的开发板芯片为EP4CE10F17C8

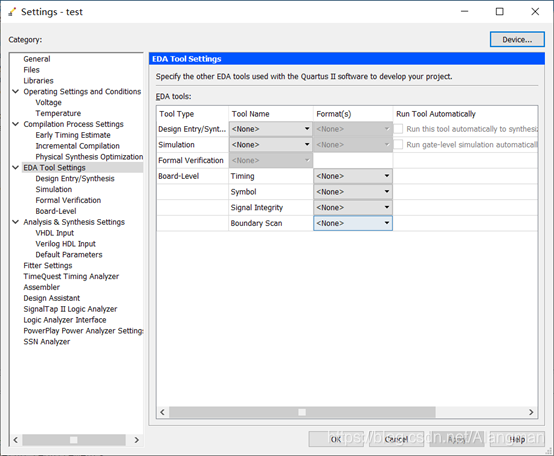

EDA Tools Settings中的仿真工具选择None,不需要自动进行波形仿真。

点击Finish

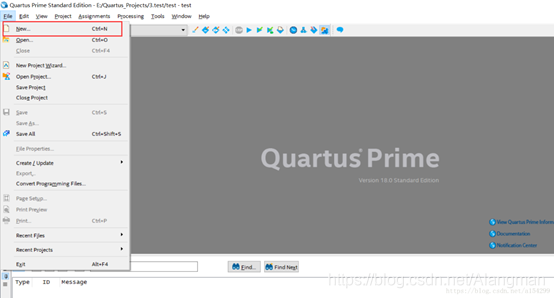

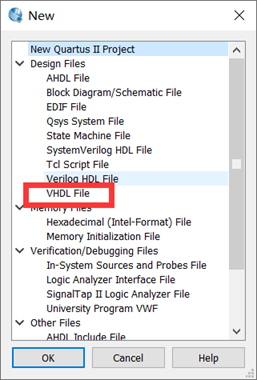

点击新建文件,选择 vhdl file

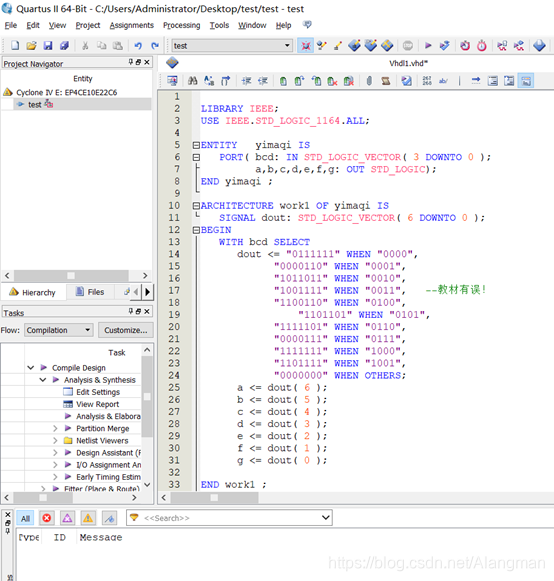

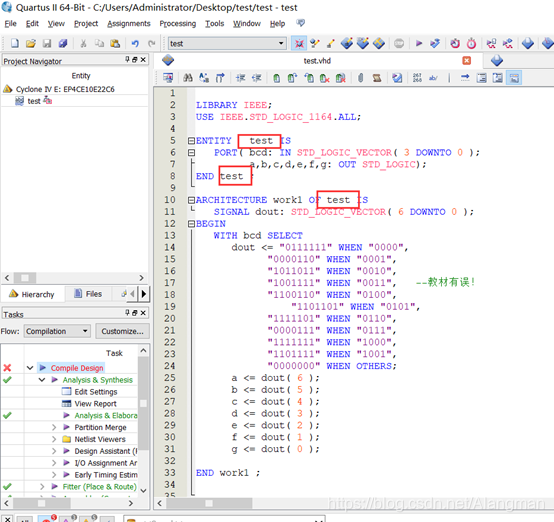

编写vhdl语言程序,以我们上次实验做的七段显示译码器为例(注意文件名和器件名一定要一致)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY yimaqi IS

PORT( bcd: IN STD_LOGIC_VECTOR( 3 DOWNTO 0 );

a,b,c,d,e,f,g: OUT STD_LOGIC);

END yimaqi ;

ARCHITECTURE work1 OF yimaqi IS

SIGNAL dout: STD_LOGIC_VECTOR( 6 DOWNTO 0 );

BEGIN

WITH bcd SELECT

dout <= "0111111" WHEN "0000",

"0000110" WHEN "0001",

"1011011" WHEN "0010",

"1001111" WHEN "0011", --教材有误!

"1100110" WHEN "0100",

"1101101" WHEN "0101",

"1111101" WHEN "0110",

"0000111" WHEN "0111",

"1111111" WHEN "1000",

"1101111" WHEN "1001",

"0000000" WHEN OTHERS;

a <= dout( 6 );

b <= dout( 5 );

c <= dout( 4 );

d <= dout( 3 );

e <= dout( 2 );

f <= dout( 1 );

g <= dout( 0 );

END work1 ;

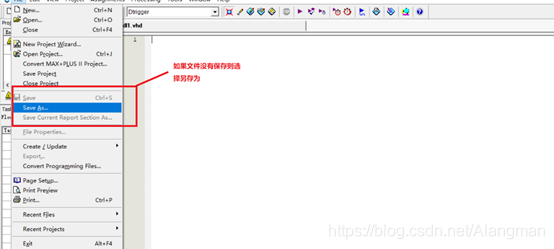

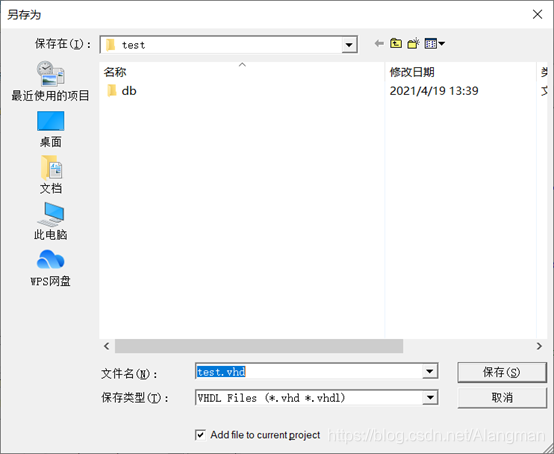

如果刚刚新建的VHDL没有保存,可以再File里选择另存为;

VHDL文件名和工程名相同;

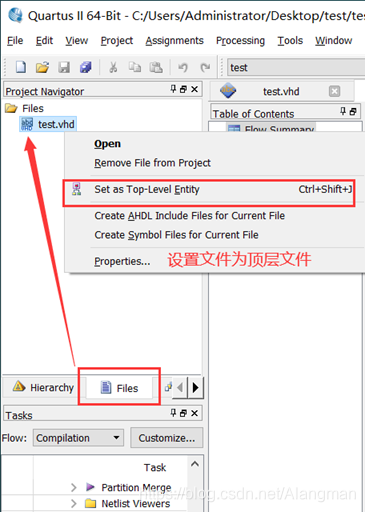

右键单击将写好的文件设置为顶层文件

点击编译,没有报错即VHDL文件编写成功

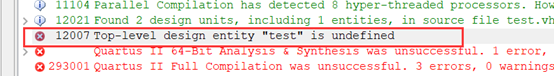

如出现以下内容,是因为项目名称叫做test,但是找不到这个名称叫test。顶级模块的名称必须与项目名称一致。

故更正程序如下所示

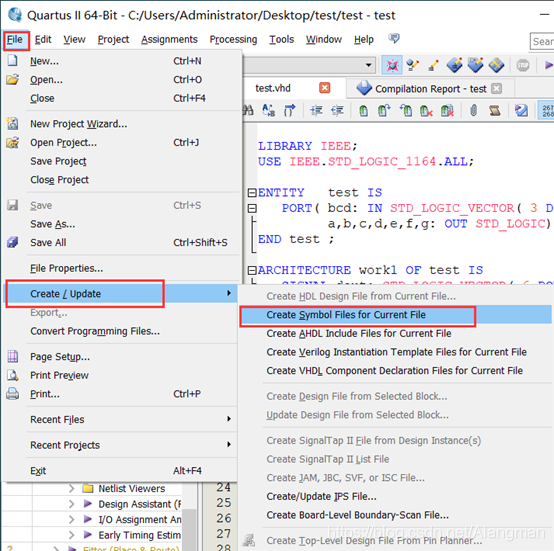

将刚才的vhdl文件生成为部件,并用它进行画图,进行如下操作:

点击 File->Create/Update->Create symbol files for current file,没有报错即可

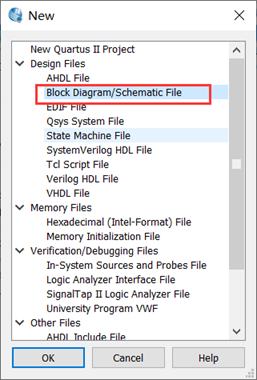

如果你想用上面的部件画一个顶层图,那么就新建一个Block Diagram/Schematic File

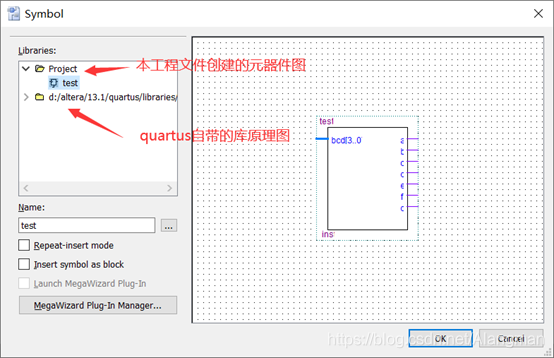

双击空白处可调出Symbol界面,在这里可以看到自己工程文件生成的部件

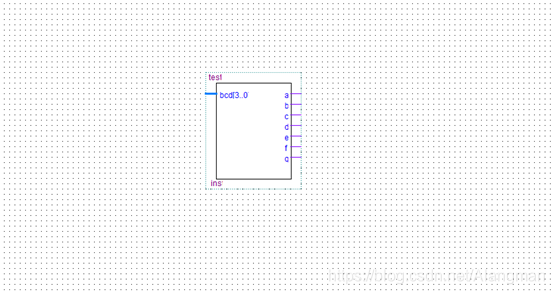

选中后点击OK即可放置在原理图上,然后进行保存即可。

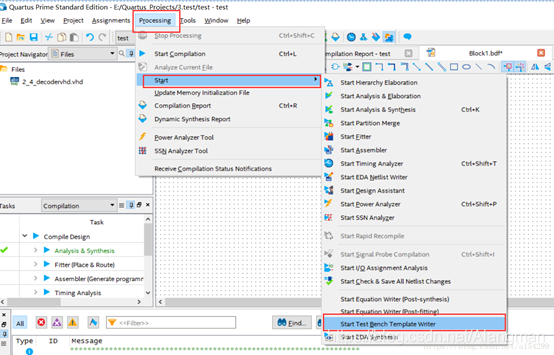

对生成的部件进行仿真测试,则进行如下操作:

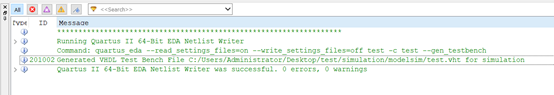

点击Processing->Start->Start Test Bench Template Writer,没有报错即可

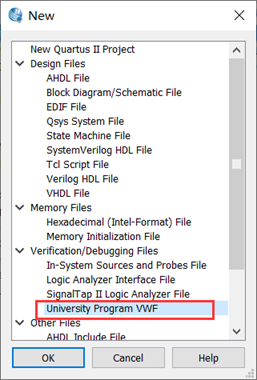

新建一个University Program VWF文件

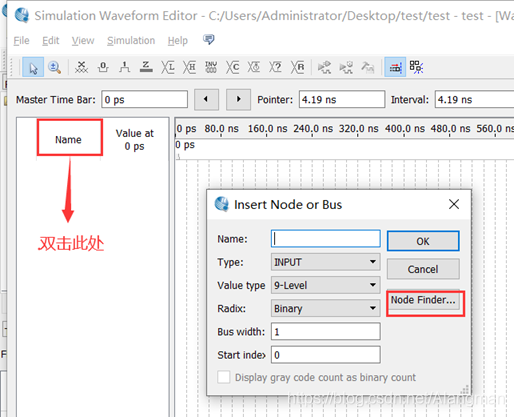

双击左侧空白处,可调出Insert Node or Bus窗口

点击list按钮就会显示出Entity(实体)定义的所有变量,之后全部导入即可;

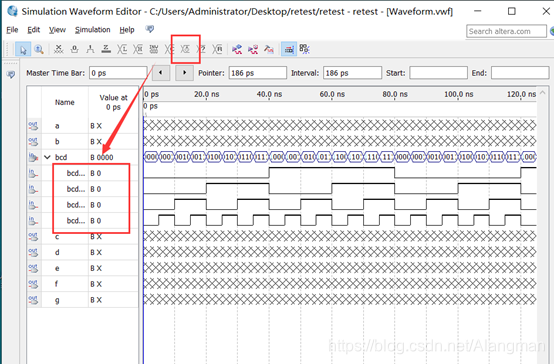

分别给四个输入信号加上激励波形,分别为10、20、40、80,满足BCD码条件

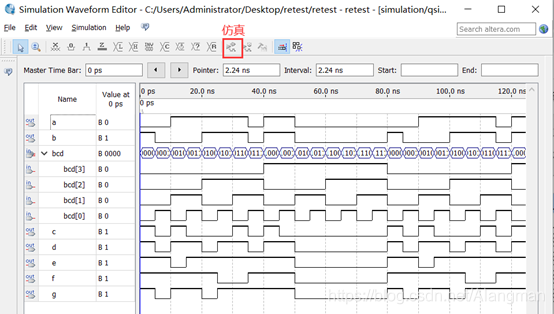

保存后点击Run Functional Simulation,稍等即可弹出仿真后的界面

【注】此处仿真不出图,很麻烦,需要新建仿真库https://blog.csdn.net/u013753393/article/details/50350138<> 参考本文

另一简便途径是,下载ModelSim-Altera。附上下载链接:https://pan.baidu.com/s/16nEjS6Tx1NHKpU_e4ale1g 提取码:1234

【注】想对哪个文件进行仿真,就需将哪个文件设置为顶层文件,并进行组建编译,然后重新建立一个VWF文件。

下一篇:如何将写的程序下入正点原子_新起点开发板

微信文件传输助手是微信电脑版与手机微信之间相互传输图片等文件的好工具,但很...

一、正则表达式概述 二、正则表达式在VBScript中的应用 三、正则表达式在VavaScr...

本文将研究 ES6 的 for ... of 循环。 旧方法 在过去,有两种方法可以遍历 javas...

一石激起千层浪,继中国区浩浩荡荡的大裁员告一段落之后,甲骨文并未因此收起手...

计算属性computed: 支持缓存,只有依赖数据发生改变,才会重新进行计算 不支持...

vbs:把一段文字中指定字符颜色变成红色的正则 functionc(Tstr,Word) Dimre Setre...

ADO对象: Connection Command Recordset Record Stream ASP支持的对象很多,可...

前言 相信大家都知道在IDE中代码的智能提示几乎都是标配,虽然一些文本编辑器也...

歌词编辑器 歌词编辑器 第一步:选择要播放的歌曲并播放 第二步:填写全部的歌词...

【排序算法】之lowb三人组冒泡、插入、选择 什么是lowb三人组 冒泡排序bubble so...