Verilog 不同编码风格对实际综合电路的影响

原创Verilog 不同编码风格对实际综合电路的影响

原创

单片机点灯小能手

发布于 2023-09-23 20:42:04

发布于 2023-09-23 20:42:04

Verilog是一种硬件描述语言(HDL),用于设计数字电路和系统。统一、良好的代码编写风格,可以提高代码的可维护性和可读性。

同样的功能,不同的Verilog 编码风格也会对综合过程产生重大影响,在综合的过程中,Verilog 代码被转换为门级电路,不同的代码风格,综合出的电路可能是不同的,对应资源的占用和功耗也会有差异。

下面以一个模3计数器为例,演示3种不同写法对综合后电路的影响。

示例 #1

module cntr_mod3 (

//Inputs

input clk,

input rstn,

//Outputs

output reg [1:0] out,

);

?

always @(posedge clk) begin

if ((!rstn) | (out[1] & out[0]))

out <= 0;

else

out <= out + 1;

end

?

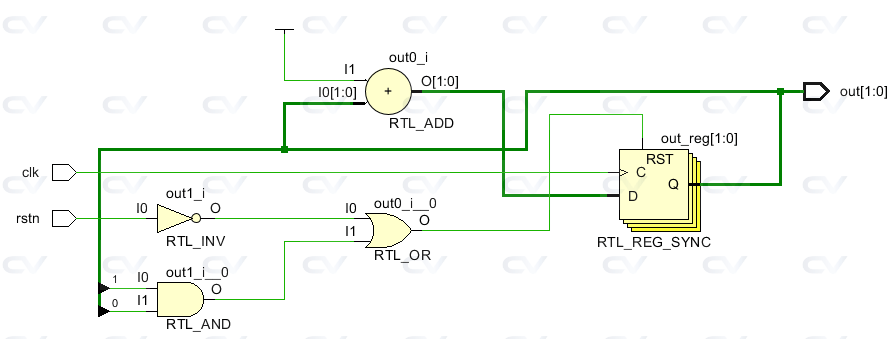

endmodule综合出的电路如下图所示,三个基本的门电路:

示例 #2

module cntr_mod3(

//Inputs

input clk,

input rstn,

//Outputs

output reg [1:0] out

);

?

always @(posedge clk) begin

if (!rstn)

out <= 0;

else begin

if (out == 3)

out <= 0;

else

out <= out + 1;

end

end

?

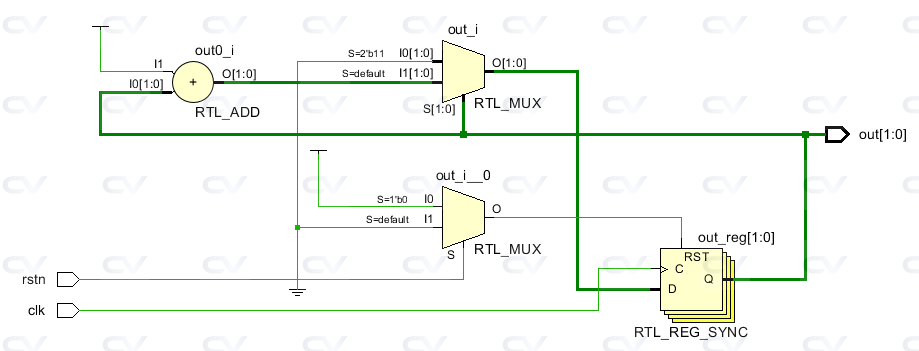

endmodule综合出了两个选择器和一个加法器,相比于前一种写法将会占用更多的资源。

示例 #3

module cntr_mod3(

//Inputs

input clk,

input rstn,

//Outputs

output reg [1:0] out

);

?

always @(posedge clk) begin

if (!rstn)

out <= 0;

else begin

if (&out)

out <= 0;

else

out <= out + 1;

end

end

?

endmodule相比于上一个写法,少了一个选择器。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

评论

登录后参与评论

推荐阅读