【自己动手画CPU】单总线CPU设计(一)

【自己动手画CPU】单总线CPU设计(一)

?1. 闯关目的

?第1关:MIPS指令译码器设计

(1) 理解指令译码的基本概念;

(2) 将32位MIPS指令字译码成不同的指令译码信号。

?第2关:定长指令周期---时序发生器FSM设计

(1) 理解传统三级时序系统中时序发生器的基本原理;

(2) 设计实现定长指令周期的时序发生器状态机以及输出函数。

?第3关:定长指令周期---时序发生器输出函数设计

(1) 理解传统三级时序系统中时序发生器的基本原理;

(2) 设计实现定长指令周期的时序发生器状态机以及输出函数。

?第4关:硬布线控制器组合逻辑单元

(1) 理解传统三级时序系统中硬布线控制器的设计原理;

(2) 设计实现硬布线控制器组合逻辑单元。

?第5关:定长指令周期---硬布线控制器设计

(1) 理解传统三级时序系统中硬布线控制器的设计原理;

(2) 设计实现定长指令周期硬布线控制器组合逻辑单元。

?第6关:定长指令周期---单总线CPU设计

(1) 理解单总线结构CPU基本原理;

(2) 设计实现定长指令周期的三级时序系统, MIPS程序能在单总线结构上运行,最终能运行简单的排序程序sort-5.hex以实现利用硬件电路对应的编解码电路。

?2. 闯关内容

?第1关:MIPS指令译码器设计

利用比较器等功能模块将32位MIPS指令字译码生成LW、SW、BEQ、SLT、ADDI、OtherInstr等指令译码信号。指令译码器是控制器核心功能部件,负责将指令字翻译成一根根的指令译码信号,每一根指令译码信号代表一条具体的指令。

?第2关:定长指令周期---时序发生器FSM设计

利用数字逻辑电路相关知识设计定长指令周期的三级时序系统,时序发生器包括状态机和输出函数两部分,本实验要求设计状态机。上一关实现了指令译码器后,就可以开始实现另外一个核心功能模块,时序发生器了,主要包括状态寄存器,状态机组合逻辑,输出函数组合逻辑三部分。其中状态机负责现态与次态的转换,输出函数根据当前状态生成状态周期电位和节拍周期电位。单总线结构中如果采用定长指令周期,所有MIPS指令都需要3个机器周期,每个机器周期4个时钟节拍,一共需要12个状态。按状态图填写相应的excel表,自动生成次态逻辑表达式后,即可在logisim中自动生成该电路。

?第3关:定长指令周期---时序发生器输出函数设计

利用数字逻辑电路相关知识设计定长指令周期的三级时序系统,时序发生器包括状态机和输出函数两部分,本实验要求设计状态机。上一关实现了指令译码器后,就可以开始实现另外一个核心功能模块,时序发生器了,时序发生器内部框图主要包括状态寄存器,状态机组合逻辑,输出函数组合逻辑三部分。其中状态机负责现态与次态的转换,输出函数根据当前状态生成状态周期电位和节拍周期电位。单总线结构中如果采用定长指令周期,所有MIPS指令都需要3个机器周期,每个机器周期4个时钟节拍,一共需要12个状态。按状态图填写相应的excel表,自动生成次态逻辑表达式后,即可在logisim中自动生成该电路。

?第4关:硬布线控制器组合逻辑单元

在实现了指令译码逻辑、时序发生器主要功能部件后,进一步设计实现控制器核心模块硬布线控制器组合逻辑单元,所有微操作控制信号都是反馈信号,指令译码信号,状态周期电位,节拍电位的组合逻辑函数。可列出所有微操作信号的产生条件,填写下面的excel表格,自动生成逻辑表达式,然后再Logisim中自动生成电路。

?第5关:定长指令周期---硬布线控制器设计

在实现指令译码、时序发生器关键功能部件、硬布线控制器等功能模块后,最终实现硬布线控制器的集成,,硬布线控制器总体框架如下图所示:

图5.1-1

其中时序发生器框架如下图:

图5.1-2

要求在硬布线控制器子电路中将时序状态机与输出函数、状态寄存器正确连接,实现时序发生器逻辑,注意只需要修改左下角方框中的逻辑,将各功能部件正确连接即可进行测试。

?第6关:定长指令周期---单总线CPU设计

完成前面所有实验关卡以后,在本关进行最终的联调,测试排序程序。在RAM中加载sort-5.hex程序,ctrl+k自动运行,程序应该运行至0xbbb节拍停下,指令计数为251,注意最后一条指令是一条beq分支指令,会跳回当前指令继续执行,是死循环。

?3. 闯关步骤

?第1关:MIPS指令译码器设计

图5.1-3

?第2关:定长指令周期---时序发生器FSM设计

图5.1-4

?第3关:定长指令周期---时序发生器输出函数设计

图5.1-5

?第4关:硬布线控制器组合逻辑单元

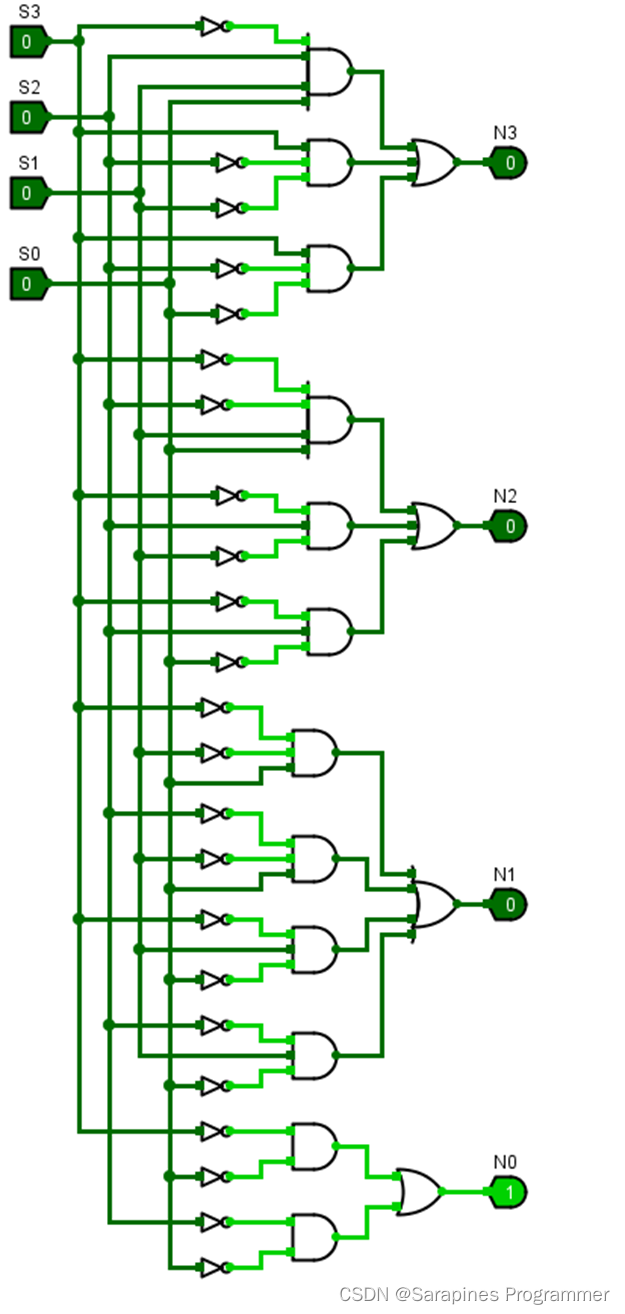

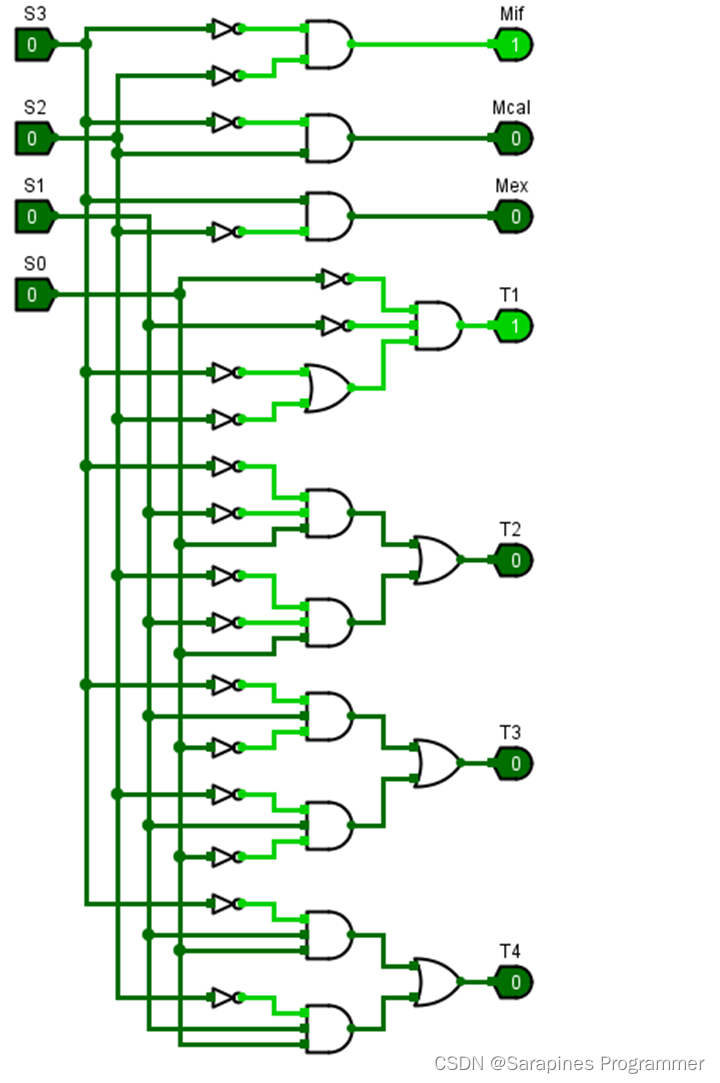

图5.1-6 左图为上半图,右图为下半图

?第5关:定长指令周期---硬布线控制器设计

图5.1-7

?第6关:定长指令周期---单总线CPU设计

图5.1-8

?4. 闯关总结

?第1关:MIPS指令译码器设计

1. 需要注意检查待测电路引脚框架是否和前面的图一致,调整引脚会引起待测部件封装接口改变,否则会导致测试无法正常进行;

2. 检查待测电路子电路外观也就是封装和前面的图是否一致,引脚位置,引脚顺序、引脚数目等,这个不一样也会导致测试无法通过。

?第2关:定长指令周期---时序发生器FSM设计

1. 点击logisim上面的工程project选择分析组合逻辑电路,按状态图填写相应的excel表,自动生成次态逻辑表达式即可在logisim中自动生成电路。需要注意的是填写真值表要注意细心,多检查就好一般不会出错。

?第3关:定长指令周期---时序发生器输出函数设计

1. 通关思路类似第2关,同样在logisim上的工程project下辖的分析组合逻辑电路处根据测试用例,填写表格。

?第4关:硬布线控制器组合逻辑单元

1. 需要注意:slt指令的执行周期输出信号为:T1:rout xin;T2:rout rs/rt slt;T3:zout rin regdst,其中rs/rt是regtgt信号,Cin是PCin(当输入equal=1,T3=1,beq时,输出PCin=1),最后将excel生成的表达式输入到logisim中。

2. 如果slt部分出错,T1部分应该将Rs/Rt信号和slt信号剔除。

?第5关:定长指令周期---硬布线控制器设计

1. 通关设计:在硬布线控制器子电路中将时序状态机与输出函数、状态寄存器正确连接,实现时序发生器逻辑。

2. 需要注意只修改左下角方框中的逻辑,将各功能部件正确连接即可进行测试。

?第6关:定长指令周期---单总线CPU设计

1. 通关设计:首先在RAM中加载sort-5.hex程序(加载数据镜像),ctrl+k自动运行,程序应该运行至0x81d节拍停下,指令计数为251。

2. 需要注意最后一条指令是一条beq分支指令,会跳回当前指令继续执行。