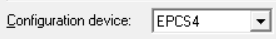

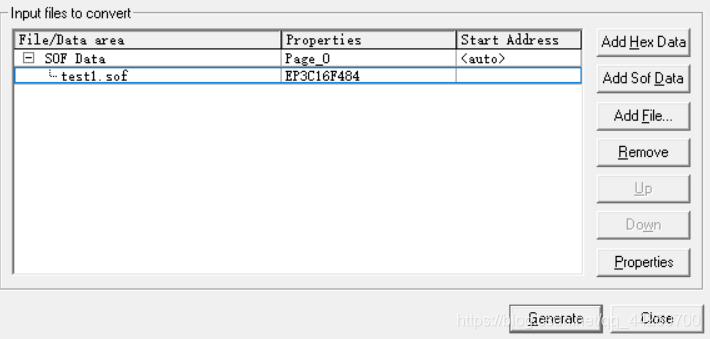

以下是如何通过AS接口进行固化的过程介绍

实验软件:quartus II 9.1

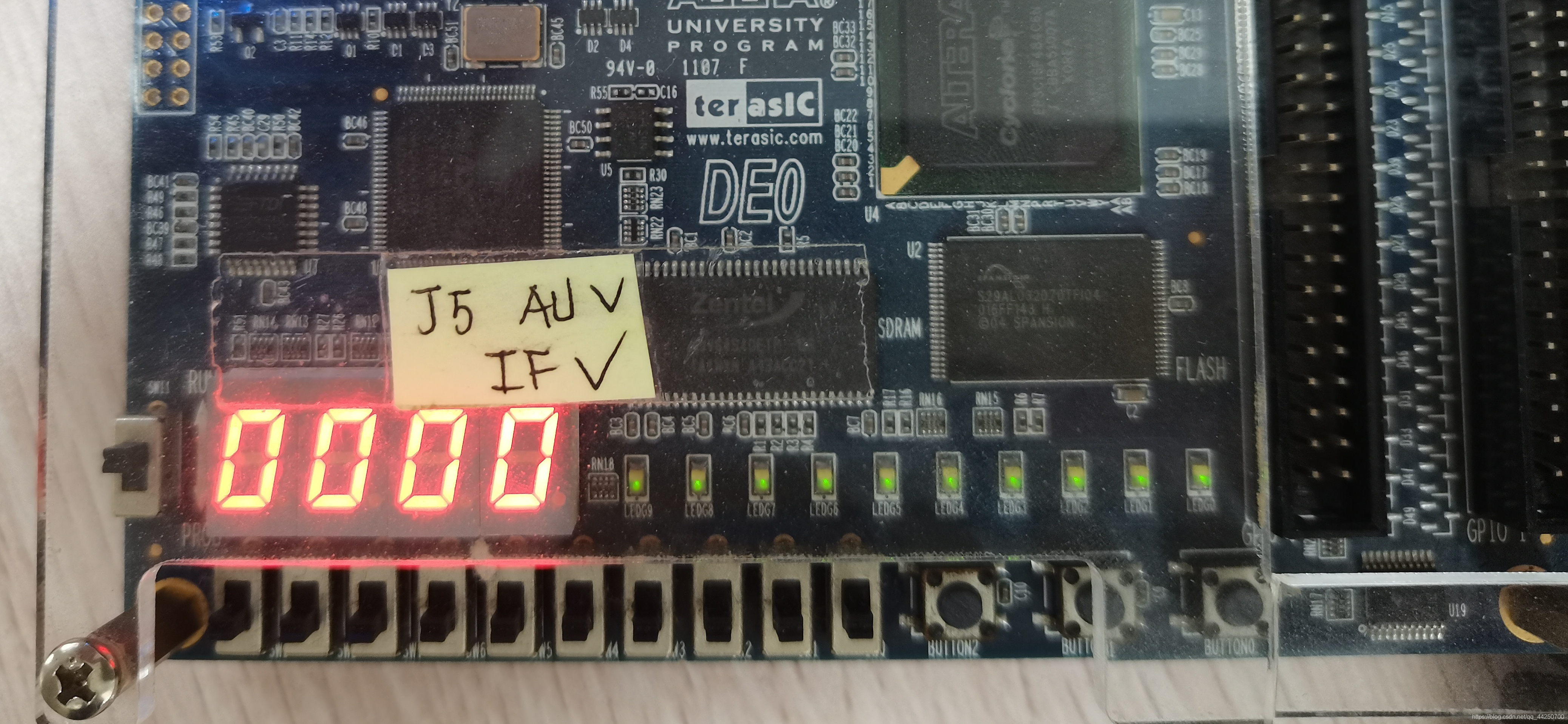

实验板子:terasic DE0

附:

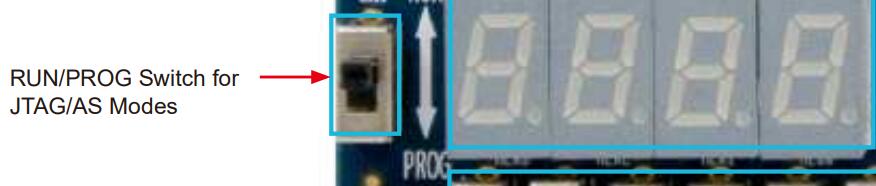

我这个实验最终想要的结果就是实现“0000”稳定常亮。下面是我这个实验的verilog HDL代码和BDF原理图。

代码

module testone(

OUT);

output [7-1:0] OUT;

reg[7-1:0] OUT;

always @(*) begin

OUT=7'b 1000000;

end endmodule

module testonee(

OUT);

output [7-1:0] OUT;

reg[7-1:0] OUT;

always @(*) begin

OUT=7'b 1000000;

end endmodule

module testoneee(

OUT);

output [7-1:0] OUT;

reg[7-1:0] OUT;

always @(*) begin

OUT=7'b 1000000;

end endmodule

module testoneeee(

OUT);

output [7-1:0] OUT;

reg[7-1:0] OUT;

always @(*) begin

OUT=7'b 1000000;

end endmodule

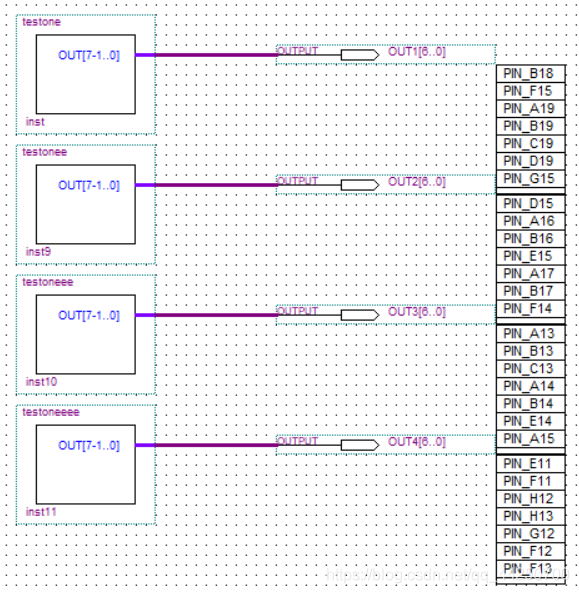

其实就是四个相同的模块并列,每个模块控制一个七段数码管。可以把四个数码管用一个模块控制。因为是恒定常亮,所以可以不用添加时钟模块。

BDF原理图

本文介绍如何终止所有用户会话、特定的用户回话。 终止所有用户会话 下面的shell...

橡皮擦一个逗趣的互联网高级网虫。新的系列让我们一起进入 Django 世界。 已经完...

内容详细标签: h1~h6标题标签 pre格式化文本 u下划线(underline) i斜体字(ita...

1. 前言 表查询,也称为多表连接查询;作为关系型数据库最主要的查询方式,在日常...

3 月 24 日消息 微软 Cortana 很快就会在 iOS 和 Android 设备上消失,现在该应...

问题 今天安装了IDEA2019.03版本,在安装插件时搜索不到插件: 解决 点击右上角...

一、主要功能 本次任务主要是使用VUE来实现一个简单的学生信息管理系统,主要功...

精致的高性能的下拉刷新上拉加载组件 mescroll --【wxs+renderjs实现】高性能的...

基于 Linux 的 Moodle 学习管理系统进行远程教学。 这次大流行对远程教育的需求...

2021届考研西北工业大学网络空间安全学院的专硕还算比较顺利吧来分享一波经验造...